-

提高早期設計周期的 LVS 驗證效率

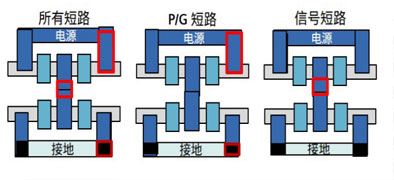

利用創新的 Calibre? nmLVS-Recon? 早期驗證工具,設計人員可以在早期設計階段對模塊、宏和芯片運行針對性的短路隔離分析和調試。Calibre nmLVS-Recon 短路隔離使用模型專註於實現快速、高效、優先的短路隔離和短路路徑調試。

下載白皮書 -

利用更高效的 LVS 調試提高生産率

RVE 實用工具可幫助設計人員更快速地調試和修複 LVS 錯誤,而且無需多次運行完整的 LVS。交互式短路隔離提供一種係統化且有優先順序的短路調試流程。純文本格式的修複建議可幫助設計人員找到 LVS 比較差異的根本原因,而在版圖和電路圖視圖中高亮顯示差異的功能讓設計人員可以更快速、更高效地實施修複措施。

下載白皮書 -

增強 IO 環檢查以實現一緻、可定製的驗證

Calibre PERC IO 環檢查框架消除了人工檢查,提供一個類似於 DRC 的強大環境,能以 signoff 級質量驗證所有 IO 佈局規則。IO 環檢查器在第一個 LEF/DEF 底層規劃上運行,可以對 IO 環佈局規則進行早期且全麵的檢查,能夠實現更改,而幾乎不會對版圖産生影響。快速準確的調試和糾正可確保 SoC IO 環不僅提供所需的保護,而且符合所有 IP 和 SoC 設計規則。

下載白皮書 -

MaxLinear和 Calibre RealTime Digital:P&R 中的Signoff DRC

MaxLinear 在底層規劃和佈局期間運用 Calibre RealTime Digital 接口實現了快速的叠代 signoff DRC 檢查和修複。他們不僅減少了批處理 DRC 的總叠代次數,而且消除了最終物理驗證 signoff 期間的潛在後期問題(其修複難度要大得多)。採用 Calibre RealTime Digital 接口能夠讓 MaxLinear 設計人員加快 DRC 收斂速度,在所有節點為所有設計的流片日程均節省數周時間。

下載白皮書 -

用於連續構建設計流程的快速版圖合並

在並行實施期間,通過對 SoC 多次運行全芯片物理驗證,設計人員可以在設計流程的早期發現並修複錯誤。了解如何建立快速、可靠的數據庫合並流程,幫助最大限度減少耗時的活動,同時確保快速、準確地解決所有設計問題。

下載白皮書 -

加快早期設計探索和驗證,縮短上市時間

早期階段芯片級物理驗證麵臨許多挑戰。Calibre? Recon 工具支持設計團隊在設計周期的早期階段(此時各種組件尚不成熟)便對整個芯片設計版圖進行分析和物理驗證。利用 Calibre Recon,設計人員可以使用晶圓代工廠/IDM Calibre sign-off 設計套件快速輕鬆地找到並解決集成問題,同時縮短 DRC 總運行時間,加快設計收斂,確保實現高質量設計。

下載白皮書