-

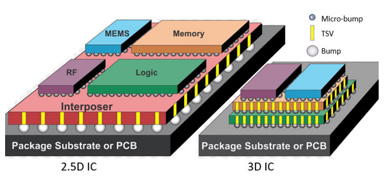

2.5D 和 3D IC 的自動化ESD 防護驗證

確保您的集成電路 (IC) 設計能夠承受靜電放電 (ESD) 事 件而不會導緻損壞或故障,這是 IC 電路設計和驗證中極 其重要的一項活動。雖然常規 2D IC 已擁有完善的自動 化 ESD 驗證流程,但 2.5D 和 3D 集成給 ESD 設計和驗證 提出了新的挑戰。盡管有一些設計方法可幫助設計人員 在 2.5D 和 3D IC 中實現有效的 ESD 防護,但迄今為止, 這些技術顯然缺乏自動化 ESD 驗證解決方案。讓我們來 看看這類集成技術所帶來的驗證挑戰,然後演練一種經 過驗證的適用於 2.5D 和 3D IC 的自動化 ESD 驗證方法。

下載白皮書 -

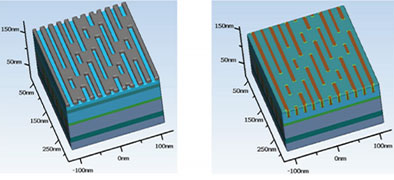

適用於 5 nm 及以下節點的多重曝光選項:SADP、SAQP、SALELE

鑒於傳統的光刻-蝕刻多重曝光工藝存在對齊控製的問題,不論使用哪種光刻技術,自對齊多重曝光工藝都已成為最先進工藝的必要條件。通過詳細的分步說明,幫助您了解 SADP、SAQP 和 SALELE 工藝。

下載白皮書 -

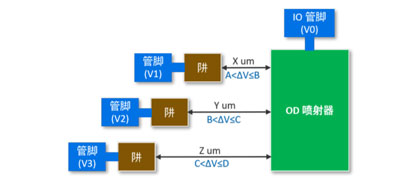

XML約束文件:編寫可靠性規則和檢查的更好方法

創建 XML 約束文件來定義規則約束及其參數,可以為規則開發人員和規則使用者簡化 Caliber PERC 可靠性規則的創建工作。規則開發人員創建規則約束和參數之後,規則使用者便可定義必要的參數值,而無需訪問規則集或了解 Calibre PERC 規則語法。使用 XML 約束文件不僅能消除規則文件的不必要重複,而且在規則檢查實現中能達到更高的一緻性和準確性。

下載白皮書 -

利用 Calibre nmLVS-Recon 技術加快上市速度:電路驗證新範式

有一個趨勢非常明顯……流片變得越來越睏難,需要的時間也越來越長。作為日益壯大的創新性早期設計驗證技術套件的一部分,Caliber nmLVS-Recon 工具使設計團隊能夠快速檢查“存在問題”和不成熟的設計,以便更快、更早地發現並修複具有重大影響的電路錯誤,從而在總體上縮短流片排程和上市時間。

下載白皮書 -

加快電源網絡 P2P 電阻調試

篩選大型電源和接地網絡或較小的信號網絡以僅高亮顯示與被檢查 P2P 結果相關的網絡部分,可以最大程度地減少資源使用和加載時間,同時提高 P2P 電阻調試效率。多種篩選器選項使設計人員可以根據需要靈活修改版圖數據。

下載白皮書